Page 57 - TSIA 2024 年會_年刊

P. 57

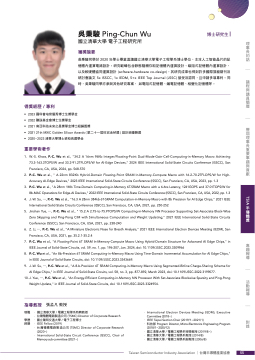

吳秉駿 Ping-Chun Wu 國立清華大學 電子工程研究所 獲獎摘要 博士研究生 吳秉駿同學於 2020 年學士畢業逕讀國立清華大學電子工程學系博士學位,主攻人工智能晶片的記 憶體內運算電路設計。研究範疇包含靜態隨機存取記憶體內運算設計、磁阻式記憶體內運算設計, 以及軟硬體協同運算設計 (software-hardware co-design),其研究成果也得到許多國際頂級期刊及 研討會論文 5x ISSCC, 1x IEDM, 5+x IEEE Top Journal (JSSC) 接受及認同,且申請多項專利。同 時,吳秉駿同學亦參與其他研究專案, 如電阻式記憶體、鐵電記憶體、相變化記憶體等。 得獎經歷 / 專利 • 2023國科會培育優秀博士生獎學金 • 2022聯詠基金會博士生獎學金 • 2021南亞科技未來之星獎學金博士組銅質獎 • 2021 21th MXIC Golden Silicon Awards ( 第二十一屆旺宏金矽獎 ) 設計組優勝獎 • 2020~2023清華大學博士班校長獎學金 重要學術著作 1. W.-S. Khwa, P.-C. Wu et al., "34.2 A 16nm 96Kb Integer/Floating-Point Dual-Mode-Gain-Cell-Computing-in-Memory Macro Achieving 73.3-163.3TOPS/W and 33.2-91.2TFLOPS/W for AI-Edge Devices," 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2024, pp. 568-570 2. P.-C. Wu et al., " A 22nm 832Kb Hybrid-Domain Floating-Point SRAM In-Memory-Compute Macro with 16.2-70.2TFLOPS/W for High- Accuracy AI-Edge Devices," 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2023, pp. 1-3 3. P.-C. Wu et al., "A 28nm 1Mb Time-Domain Computing-in-Memory 6T-SRAM Macro with a 6.6ns Latency, 1241GOPS and 37.01TOPS/W for 8b-MAC Operations for Edge-AI Devices," 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2022, pp. 1-3 4. J.-W. Su, ⋯, P.-C. Wu et al., "16.3 A 28nm 384kb 6T-SRAM Computation-in-Memory Macro with 8b Precision for AI Edge Chips," 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2021, pp. 250-252 5. Jinshan Yue, ⋯, P.-C. Wu et al., " 15.2 A 2.75-to-75.9TOPS/W Computing-in-Memory NN Processor Supporting Set-Associate Block-Wise Zero Skipping and Ping-Pong CIM with Simultaneous Computation and Weight Updating," 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2021, pp. 238-240 6. Z. Li, ⋯, P.-C. Wu et al., "A Miniature Electronic Nose for Breath Analysis," 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2021, pp. 35.2.1-35.2.4 7. P.-C. Wu et al., "A Floating-Point 6T SRAM In-Memory-Compute Macro Using Hybrid-Domain Structure for Advanced AI Edge Chips," in IEEE Journal of Solid-State Circuits, vol. 59, no. 1, pp. 196-207, Jan. 2024, doi: 10.1109/JSSC.2023.3309966 8. P.-C.Wuetal.,"An8b-Precision6TSRAMComputing-in-MemoryMacroUsingTime-DomainIncrementalAccumulationforAIEdgeChips," in IEEE Journal of Solid-State Circuits, doi: 10.1109/JSSC.2023.3343669. 9. J.-W. Su, ⋯, P.-C. Wu et al., "A 8-b-Precision 6T SRAM Computing-in-Memory Macro Using Segmented-Bitline Charge-Sharing Scheme for AI Edge Chips," in IEEE Journal of Solid-State Circuits, vol. 58, no. 3, pp. 877-892, March 2023, doi: 10.1109/JSSC.2022.3199077. 10.J. Yue, ⋯, P.-C. Wu et al., "An Energy-Efficient Computing-in-Memory NN Processor With Set-Associate Blockwise Sparsity and Ping-Pong Weight Update," in IEEE Journal of Solid-State Circuits, doi: 10.1109/JSSC.2023.3324954. 指導教授 張孟凡 教授 現職 ・ 國立清華大學 / 電機工程學系特聘教授 ・ 台灣積體電路製造公司 (TSMC) Director of Corporate Research 學歷 ・ 國立陽明交通大學 / 電子工程博士 經歷 ・ IEEE Fellow (2019) ・ 台灣積體電路製造公司 (TSMC) Director of Corporate Research (2020~) ・ International Solid-State Circuit Conference (ISSCC), Chair of Memory sub-committee (2021~) ・ International Electron Devices Meeting (IEDM), Executive Committee (2018~) ・ IEEE Taipei Section Chair (2019/1~2021/1) ・ 科技部 Program Director, Micro-Electronics Engineering Program (2018/1~2020/12) ・ 國立清華大學 / 電機工程學系特聘教授 (2019/8~) ・ 國立清華大學 / 電機工程學系教授 (2014/8) ・ 國立清華大學 / 電機工程學系副教授 (2006/8) Taiwan Semiconductor Industry Association ┃台灣半導體產業協會 55 理事長的話 議程與講員簡歷 歷屆理事長重要事蹟與貢獻 TSIA 半導體獎 專題報導 活動報導 附錄